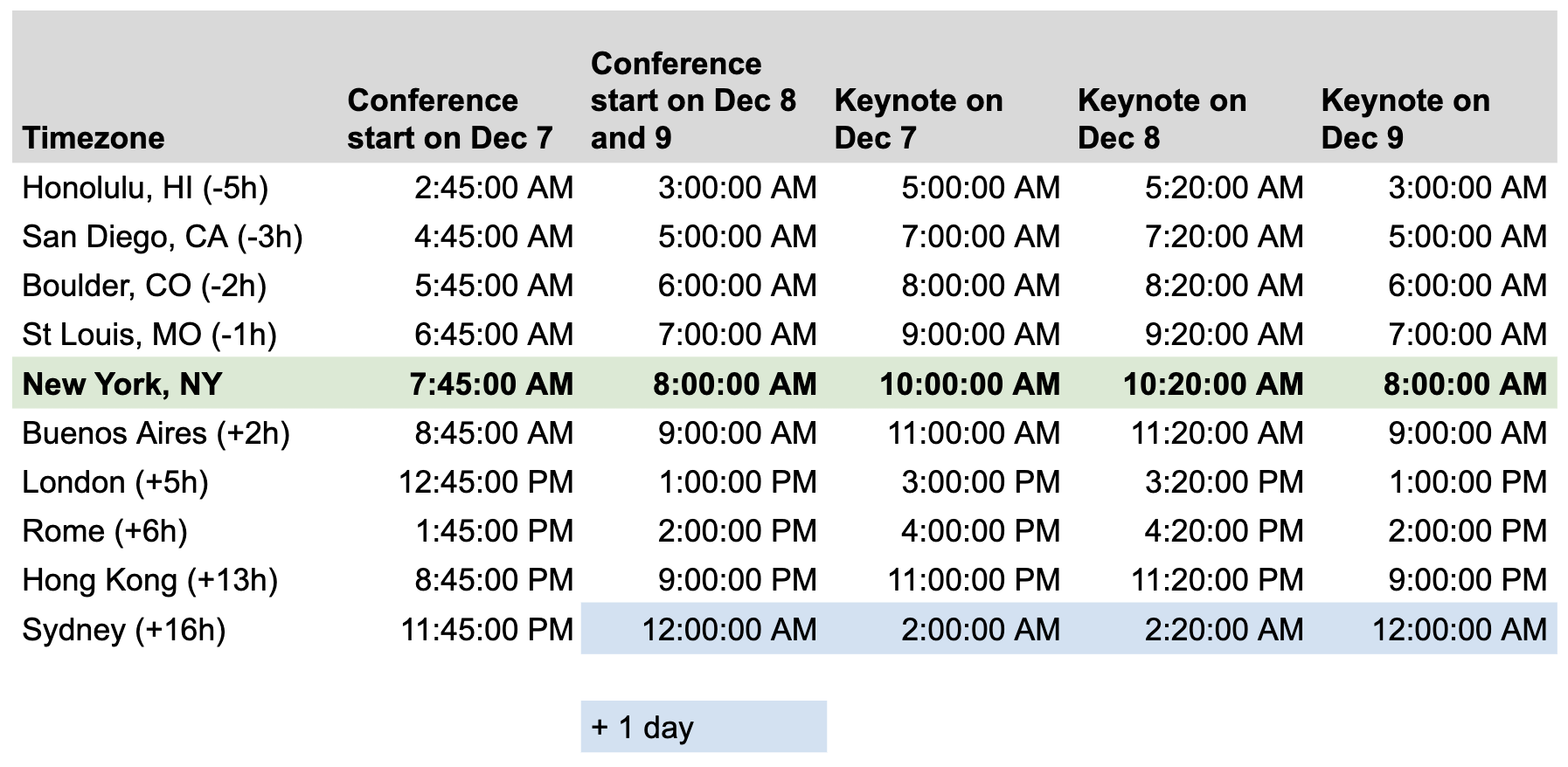

Admission Items |

||||

|---|---|---|---|---|

| Paper Author Full Conference | Early (until Nov 27, 2022) | |||

| Non-Member | US$250 | |||

| ACM/IEEE Member | US$200 | |||

| Student Non-Member | Non-applicable | |||

| Student ACM/IEEE Member | Non-applicable | |||

| Full Conference | Early (until Nov 27, 2022) | Standard (until Dec. 1, 2022) | Late (after Dec. 1, 2022) | |

| Non-Member | US$250 | US$300 | US$350 | |

| ACM/IEEE Member | US$200 | US$250 | US$300 | |

| Student Non-Member | US$50 | US$60 | US$70 | |

| Student ACM/IEEE Member | US$40 | US$50 | US$60 | |

Optional Items |

||||

| Extra Paper Registration | Early (until Nov 27, 2022) | |||

| Non-Member | US$250 | |||

| ACM/IEEE Member | US$200 | |||

| Student Non-Member | Non-applicable | |||

| Student ACM/IEEE Member | Non-applicable | |||

Exploiting unconventional physical properties, several nanodevices showed an alternative to Moore’s Law by the increase of their functionality rather than the pure scaling. Innovative device behaviors transduce to new circuit/architecture opportunities.

Exploiting unconventional physical properties, several nanodevices showed an alternative to Moore’s Law by the increase of their functionality rather than the pure scaling. Innovative device behaviors transduce to new circuit/architecture opportunities.

Here, we will introduce Three-Independent-Gate Field Effect Transistors (TIGFETs), a novel class of computation devices, that can, depending on the bias applied to its gate, achieve different modes of operations usually not achievable in a single device. The demonstrated modes of operations are (i) the dynamic reconfiguration of the device polarity; (ii) the dynamic control of the threshold voltage; and (iii) the dynamic control of the subthreshold slope beyond the thermal limit (with a measured steep slope of 6mV/dec over 5 decades of current). I will show both a silicon-based process route and a 2D approach based on WSe2 crystals. Such properties are highly desirable for logic computation. For instance, controllable-polarity devices are logical bi-conditional on both gate values and enable a compact realization of XOR-based logic functions, which are not implementable in CMOS in a compact form. Hyper regular architectures and new EDA tools are then needed to leverage the intrinsic properties of controllable-polarity devices from an application perspective.

In this talk, I will cover the different aspects of the design with TIG devices ranging from device fabrication to logic synthesis tools, emphasizing on the importance for interdisciplinary teams in the field of emerging technologies.

Short Bio: Pierre-Emmanuel Gaillardon is an Associate Professor and an adjunct Associate Professor in the School of Computing at The University of Utah, Salt Lake City, UT, where he leads the Laboratory for NanoIntegrated Systems (LNIS). He holds an Electrical Engineer M.Sc. degree from CPE-Lyon, France (2008), a M.Sc. degree in Electrical Engineering from INSA Lyon, France (2008) and a Ph.D. degree in Electrical Engineering from CEA-LETI, Grenoble, France and the University of Lyon, France (2011).

Prior to joining the University of Utah, he was a research associate at the Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland within the Laboratory of Integrated Systems (Prof. De Micheli) and a visiting research associate at Stanford University, Palo Alto, CA, USA. Previously, he was research assistant at CEA-LETI, Grenoble, France. Prof. Gaillardon is recipient of the C-Innov 2011 best thesis award, the Nanoarch 2012 best paper award, the BSF 2017 Prof. Pazy Memorial Research Award, the 2017 NSF CAREER award, the 2018 IEEE CEDA Pederson Award, the 2018 ChemE Education William H. Corcoran best paper award, the 2019 DARPA Young Faculty Award, the 2019 IEEE CEDA Ernest S. Kuh Early Career Award and the 2020 ACM SIGDA Outstanding New Faculty Award, and the 2022 ECE Department Research Award. He is a senior member of the IEEE. Prof. Gaillardon is also co-founder and CTO of RapidSilicon, an AI-enable FPGA provider and promoter of open-source technologies.

The research activities and interests of Prof. Gaillardon are currently focused on the development of novel computing systems exploiting emerging device technologies and novel EDA techniques.

Data-hungry applications demand increasing capacity and computational performance under low-power constraints. We face physical limits in further scaling down current silicon transistors. Contemporary architectures do not support faster communication between system components. There is hope in Heterogeneous Integration (HI): innovative three dimensional arrangements of individual chips based on starkly different technologies, silicon and non-silicon devices made of emerging materials, all integrated together into high-level systems.

Data-hungry applications demand increasing capacity and computational performance under low-power constraints. We face physical limits in further scaling down current silicon transistors. Contemporary architectures do not support faster communication between system components. There is hope in Heterogeneous Integration (HI): innovative three dimensional arrangements of individual chips based on starkly different technologies, silicon and non-silicon devices made of emerging materials, all integrated together into high-level systems.

Assimilating diverse technologies, architectures, and materials has enormous potential — but we face enormous implementation and design challenges. New, more efficient EDA tools based on new paradigms must take full advantage of these technologies. We will explore 3D heterogeneous ICs, their benefits and challenges, and their future potential.

Short Bio: Malgorzata Chrzanowska-Jeske is a Professor at the Electrical and Computer Engineering Department at Portland State University, and was department chair 2004-2010. She earned her M.S. from the Technical University of Warsaw, Poland, and her PhD in Electrical Engineering from Auburn University.

Her research interests include CAD for VLSI ICs, MS-SOCs, 3D ICs, nanotechnology and nano/bio systems, design for manufacturability and design issues in emerging technologies. She has given numerous plenary, keynote, and tutorial lectures at various IEEE conferences worldwide. She serves on the editorial boards of IEEE Transactions on Nanotechnology, Now Publishers’ Foundations and Trends in Integrated Circuits and Systems, and IOP Nano Express. Over the years she has served on the editorial boards of IEEE CASS II and Journal on Emerging and Selected Topics in Circuits and Systems, and as a Guest Editor for IEEE TNANO, Nanotechnology Magazine, IEEE TCAS II and other journals. She is IEEE Nanotechnology Council VP for Finances and serves on IEEE TAB Award and Recognition Committee. Previously, she served as IEEE NTC VP for Technical Activities, member of IEEE CASS BoG, and on numerous organizational, technical, and steering committees of major international conferences. She received the IEEE CEDA 2008 Donald O. Pederson Best Paper Award for the paper published in IEEEE Transactions on CAD, and the 1990 Best IEEE Transactions Paper Award from the Alabama Section. In 1993, she was awarded “Women of Distinction in Engineering Award” by Columbia Girl Scout Council. While working at the Institute of Electron Technology in Warsaw, Poland, she was a recipient of First Level Award of the Polish Ministry (Department) of Science, Higher Education and Technology for developing and Implementing NMOS-LOCOS technology for VLSI ICs (highest industrial award in Poland at that time).

In the era of ‘big data’ and ‘Internet of Things’, the traditional computing architecture based on CMOS hardware has become increasingly inefficient to support Artificial Intelligence (AI) and Machine Learning (ML), which necessitates some emerging technologies, such as memristive technology. Memristive technology was initially developed for the next-generation nonvolatile memories, for which there are still some remaining challenges to be overcome before a large-scale commercialization is feasible. On the other hand, computing applications are less constrained by such challenges and represent low-hanging fruits for memristor applications. I will first introduce the development status of memristive devices, as well as the challenges and possible solutions for those devices used for computing applications. I will then discuss a few experimental implementations of such applications with different levels of bio-inspiration.

In the era of ‘big data’ and ‘Internet of Things’, the traditional computing architecture based on CMOS hardware has become increasingly inefficient to support Artificial Intelligence (AI) and Machine Learning (ML), which necessitates some emerging technologies, such as memristive technology. Memristive technology was initially developed for the next-generation nonvolatile memories, for which there are still some remaining challenges to be overcome before a large-scale commercialization is feasible. On the other hand, computing applications are less constrained by such challenges and represent low-hanging fruits for memristor applications. I will first introduce the development status of memristive devices, as well as the challenges and possible solutions for those devices used for computing applications. I will then discuss a few experimental implementations of such applications with different levels of bio-inspiration.

Short Bio: J. Joshua Yang is a professor of the Department of Electrical and Computer Engineering at the University of Southern California. He was a professor of the ECE department at the University of Massachusetts Amherst between 2015 and 2020. He spent about 8 years at HP Labs between 2007 and 2015, leading the emerging devices team for memory and computing. His current research interest is Post-CMOS hardware for neuromorphic computing, machine learning and artificial intelligence, where he published several pioneering papers and holds 120 granted and about 60 pending US Patents. He is the Founding Chair of the IEEE Neuromorphic Computing Technical Committee, a recipient of the Powell Faculty Research Award and a recipient of UMass distinguished faculty lecturer and UMass Chancellor's Medal. He serves on the Advisory Boards of a number of prime international journals and conferences, including serving as an associate editor of Science Advances. Dr. Yang is a Clarivate™ Highly Cited Researcher in the field of Cross-Field and an IEEE fellow for his contributions to resistive switching materials and devices for nonvolatile memory and neuromorphic computing.

Abstract: Spiking neural network hardware offers a high performance, power-efficient and robust platform for the processing of complex data. Many of these systems require supervised learning, which poses a challenge when using gradient-based algorithms due to the discontinuous properties of SNNs. Memristor based hardware can offer gains in portability, power reduction, and throughput efficiency when compared to pure CMOS. This paper proposes a memristor-based spiking Liquid State Machine. The inherent dynamics of the LSM permit the use of supervised learning without backpropagation for weight updates. To carry out the design space evaluation of the LSM for optimal hardware performance, several temporal signal classification tasks are performed. It is found that the binary neuron activations in the output layer improve testing accuracy by 3.7% and 5% for classification, while reducing training time. A power and energy analysis of the proposed hardware is presented, resulting in an approximately 50% reduction in power consumption and cycle energy.